- 您现在的位置:买卖IC网 > Sheet目录345 > MT48H32M16LFB4-75B IT:C (Micron Technology Inc)IC SDRAM 512MB 54VFBGA

�� ��

��

��

��512Mb:� 32� Meg� x� 16,� 16� Meg� x� 32� Mobile� SDRAM�

�Commands�

�Commands�

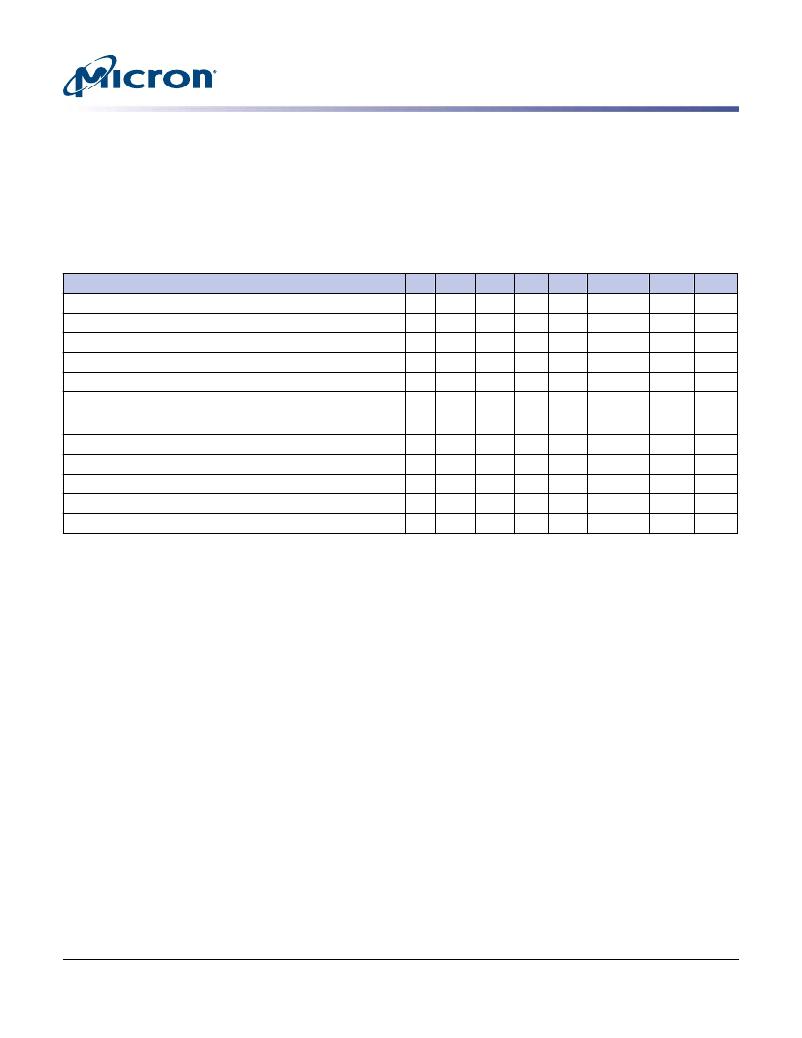

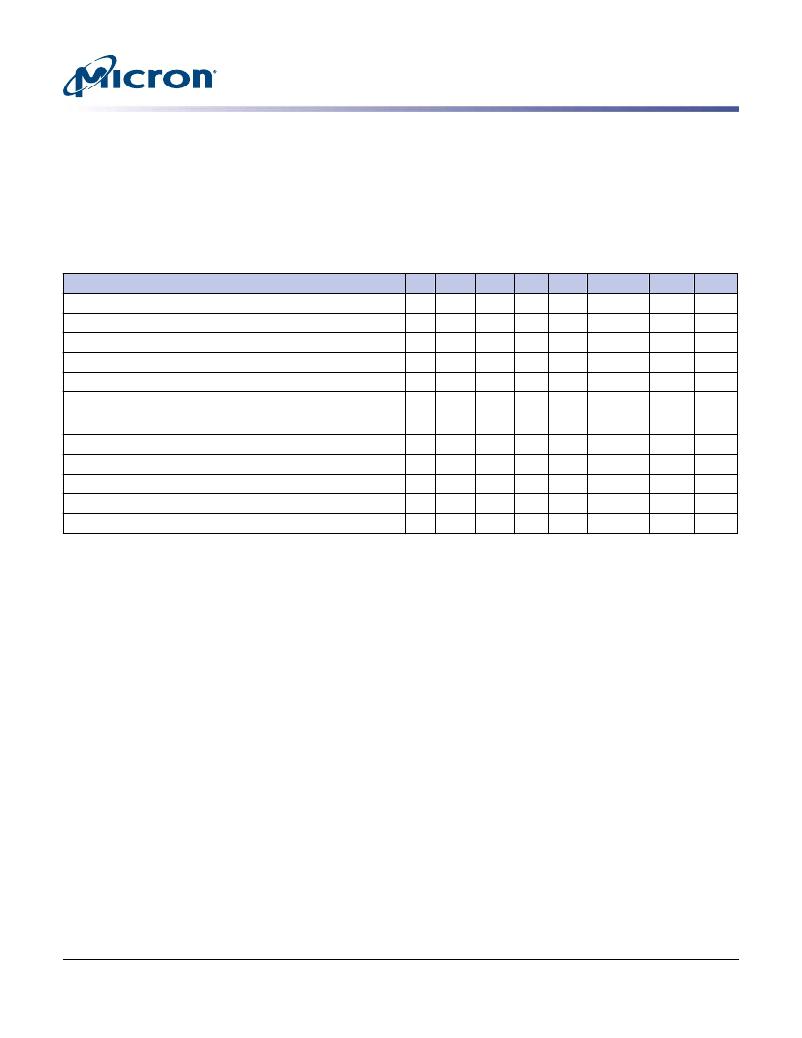

�The� following� table� provides� a� quick� reference� of� available� commands,� followed� by� a�

�written� description� of� each� command.� Additional� Truth� Tables� (Table� 18� (page� 33),� Ta-�

�ble� 19� (page� 35),� and� Table� 20� (page� 37))� provide� current� state/next� state� informa-�

�tion.�

�Table� 17:� Truth� Table� –� Commands� and� DQM� Operation�

�Note� 1� applies� to� all� parameters� and� conditions�

�Name� (Function)�

�CS# RAS# CAS# WE# DQM�

�ADDR�

�DQ�

�Notes�

�COMMAND� INHIBIT� (NOP)�

�NO� OPERATION� (NOP)�

�H�

�L�

�X�

�H�

�X�

�H�

�X�

�H�

�X�

�X�

�X�

�X�

�X�

�X�

�ACTIVE� (select� bank� and� activate� row)�

�READ� (select� bank� and� column,� and� start� READ� burst)�

�WRITE� (select� bank� and� column,� and� start� WRITE� burst)�

�BURST� TERMINATE� or� deep� power-down�

�L�

�L�

�L�

�L�

�L�

�H�

�H�

�H�

�H�

�L�

�L�

�H�

�H�

�H�

�L�

�L�

�X�

�L/H�

�L/H�

�X�

�Bank/row�

�Bank/col�

�Bank/col�

�X�

�X�

�X�

�Valid�

�X�

�2�

�3�

�3�

�4,� 5�

�(enter� deep� power-down� mode)�

�PRECHARGE� (Deactivate� row� in� bank� or� banks)�

�AUTO� REFRESH� or� SELF� REFRESH� (enter� self� refresh� mode)�

�LOAD� MODE� REGISTER�

�Write� enable/output� enable�

�Write� inhibit/output� High-Z�

�L�

�L�

�L�

�X�

�X�

�L�

�L�

�L�

�X�

�X�

�H�

�L�

�L�

�X�

�X�

�L�

�H�

�L�

�X�

�X�

�X�

�X�

�X�

�L�

�H�

�Code�

�X�

�Op-code�

�X�

�X�

�X�

�X�

�X�

�Active�

�High-Z�

�6�

�7,� 8�

�9�

�10�

�10�

�Notes:�

�1.� CKE� is� HIGH� for� all� commands� shown� except� SELF� REFRESH� and� DEEP� POWER-DOWN.�

�2.� A[0� :n� ]� provide� row� address� (where� A� n� is� the� most� significant� address� bit),� BA0� and� BA1�

�determine� which� bank� is� made� active.�

�3.� A[0� :i� ]� provide� column� address� (where� i� =� the� most� significant� column� address� for� a� given�

�device� configuration).� A10� HIGH� enables� the� auto� precharge� feature� (nonpersistent),�

�while� A10� LOW� disables� the� auto� precharge� feature.� BA0� and� BA1� determine� which�

�bank� is� being� read� from� or� written� to.�

�4.� This� command� is� BURST� TERMINATE� when� CKE� is� HIGH� and� DEEP� POWER-DOWN� when�

�CKE� is� LOW.�

�5.� The� purpose� of� the� BURST� TERMINATE� command� is� to� stop� a� data� burst,� thus� the� com-�

�mand� could� coincide� with� data� on� the� bus.� However,� the� DQ� column� reads� a� “Don’t�

�Care”� state� to� illustrate� that� the� BURST� TERMINATE� command� can� occur� when� there� is�

�no� data� present.�

�6.� A10� LOW:� BA0,� BA1� determine� the� bank� being� precharged.� A10� HIGH:� all� banks� pre-�

�charged� and� BA0,� BA1� are� “Don’t� Care.”�

�7.� This� command� is� AUTO� REFRESH� if� CKE� is� HIGH,� SELF� REFRESH� if� CKE� is� LOW.�

�8.� Internal� refresh� counter� controls� row� addressing;� all� inputs� and� I/Os� are� “Don’t� Care”� ex-�

�cept� for� CKE.�

�9.� A[11:0]� define� the� op-code� written� to� the� mode� register.�

�10.� Activates� or� deactivates� the� DQ� during� WRITEs� (zero-clock� delay)� and� READs� (two-clock�

�delay).�

�PDF:� 09005aef8459c827�

�512mb_mobile_sdram_y67m_at.pdf� –� Rev.� B� 3/11� EN�

�27�

�Micron� Technology,� Inc.� reserves� the� right� to� change� products� or� specifications� without� notice.�

�?� 2011� Micron� Technology,� Inc.� All� rights� reserved.�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MT48H8M16LFB4-75 IT:K TR

IC SDRAM 128MBIT 133MHZ 54VFBGA

MTC100-JA2-P34

CONTACT INSERT PIN

MX841BE

IC CONVERTER WHITE LED 8-SOIC

MXHV9910BTR

IC LED DRIVER HIGH BRIGHT 8-SOIC

MXN12FB12F

MOTOR BRUSHED DC 12V 2922RPM

MXN13FB08B1

MOTOR BRUSHED DC 8V 4714RPM

N01L63W2AB25I

IC SRAM ASYNC 1MBIT ULP 48-BGA

N01L63W3AB25I

IC SRAM 1MBIT 3V LP 48-BGA

相关代理商/技术参数